Module hard_fifo

This document contains technical documentation for the hard_fifo module.

To browse the source code, visit the repository on GitHub.

This module contains wrappers around the hard FIFO primitives in the Xilinx Ultrascale+ series

of devices.

Since the code depends on Xilinx primitives, the unisim library must be compiled and available

in order to simulate this module.

If this is not possible/desirable in your environment, the module can be excluded with the

names_avoid argument to tsfpga.module.get_modules() if you are using tsfpga.

Using the Vivado simulation libraries can easily be enabled in tsfpga though, by following the

guide at Vivado simulation libraries.

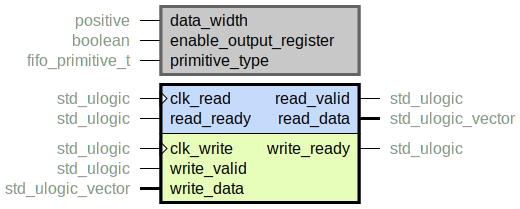

asynchronous_hard_fifo.vhd

Asynchronous (two clocks) First In First Out (FIFO) data buffering stage with AXI-Stream-like handshaking interface. This is a wrapper around the Xilinx hard FIFO primitive, and can only be used in certain devices.

Resource utilization

This entity has netlist builds set up with automatic size checkers in module_hard_fifo.py. The following table lists the resource utilization for the entity, depending on generic configuration.

Generics |

Total LUTs |

FFs |

RAMB36 |

Maximum logic level |

|---|---|---|---|---|

data_width = 18 enable_output_register = False |

3 |

1 |

1 |

2 |

data_width = 32 enable_output_register = True |

3 |

1 |

1 |

2 |

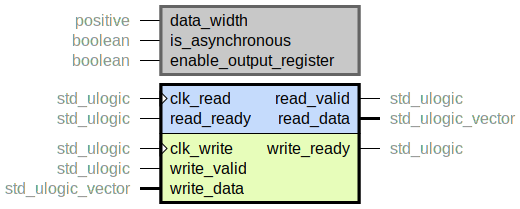

fifo36e2_wrapper.vhd

Wrapper around the Xilinx UltraScale+ FIFO36E2 primitive, with convenient AXI-Stream-like interface.

Note

The almost_full / almost_empty signals from the FIFO seem to work well. They are not

routed out at the moment since they do not have a simulation test case.

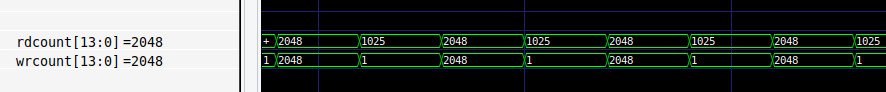

Warning

The level signal from the FIFO is not routed either.

This is because there appears to be glitches in the read/write count signals:

Hopefully this is only an issue with the unisim simulation model, and works

correctly in the hardware.

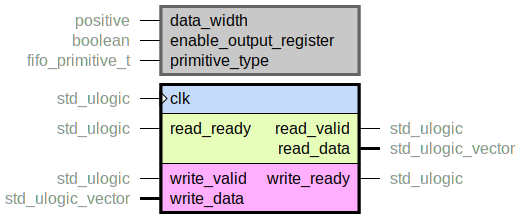

hard_fifo.vhd

Synchronous (one clock) First In First Out (FIFO) data buffering stage with AXI-Stream-like handshaking interface. This is a wrapper around the Xilinx hard FIFO primitive, and can only be used in certain devices.

Resource utilization

This entity has netlist builds set up with automatic size checkers in module_hard_fifo.py. The following table lists the resource utilization for the entity, depending on generic configuration.

Generics |

Total LUTs |

FFs |

RAMB36 |

Maximum logic level |

|---|---|---|---|---|

data_width = 18 enable_output_register = False |

3 |

1 |

1 |

2 |

data_width = 32 enable_output_register = True |

3 |

1 |

1 |

2 |

hard_fifo_pkg.vhd

Package with functions for the hard FIFO wrappers.