Module axi_stream

This document contains technical documentation for the axi_stream module.

To browse the source code, visit the repository on GitHub.

This module contains a set of AXI-Stream components written in VHDL. They are based around record types in axi_stream_pkg.vhd that make it convenient to work with the AXI-Stream signals.

See also the Module bfm for tools to efficiently simulate your AXI-Stream design.

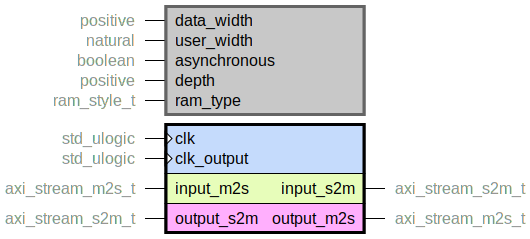

axi_stream_fifo.vhd

FIFO for AXI Stream. Can be used as clock crossing by setting the asynchronous generic.

By setting the width generics, the bus is packed optimally so that no unnecessary resources

are consumed.

Note

If asynchronous operation is enabled, the constraints of asynchronous_fifo.vhd must be used.

axi_stream_pkg.vhd

Data types for working with AXI4-Stream interfaces. Based on the document “ARM IHI 0051A (ID030610) AMBA 4 AXI4-Stream Protocol Specification” Available here: https://developer.arm.com/documentation/ihi0051/a/