Module simple_dma

This document contains technical documentation for the simple_dma module.

This module has a register interface, so make sure to study the register interface documentation as well as this top-level document.

To browse the source code, visit the repository on GitHub.

This module contains an incredibly simplified Direct Memory Access (DMA) component for streaming data from FPGA to DDR memory over AXI. Being simplified, it has the following limitations:

Can only handle writing to continuous ring buffer space in DDR. Has no scatter-gather capability.

Does not support data strobing or narrow AXI transfers. All addresses must be aligned with the AXI data width.

Each streaming beat becomes an AXI burst, giving poor AXI performance if data rate is high. This will be fixed in the future with the

packet_length_beatsgeneric.Stream data width must be the same as AXI data width. This will be fixed in the future with the

stream_data_widthandaxi_data_widthgenerics.Has no “event aggregator” feature for the

write_doneinterrupt bit. Meaning an interrupt will be generated for each beat, which can bog down software if data rate is high. This will be implemented in the future with thewrite_done_aggregate_countandwrite_done_aggregate_ticksgenerics.

Register interface

This module has register definitions.

Please see separate HTML page for register documentation.

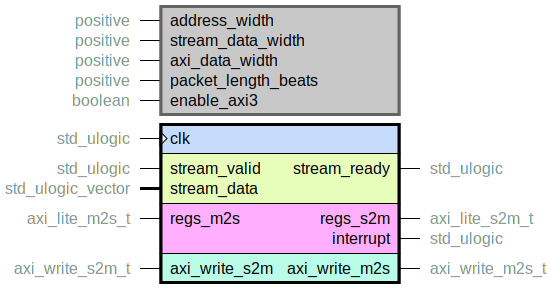

simple_dma_axi_lite.vhd

Top level for the simple DMA module, with an AXI-Lite register interface. This top level is suitable for instantiation in a user design. It integrates simple_dma_core.vhd and an AXI-Lite register file.

Resource utilization

This entity has netlist builds set up with automatic size checkers in module_simple_dma.py. The following table lists the resource utilization for the entity, depending on generic configuration.

Generics |

Total LUTs |

FFs |

Maximum logic level |

|---|---|---|---|

address_width = 29 stream_data_width = 64 axi_data_width = 64 burst_length_beats = 1 |

232 |

279 |

15 |

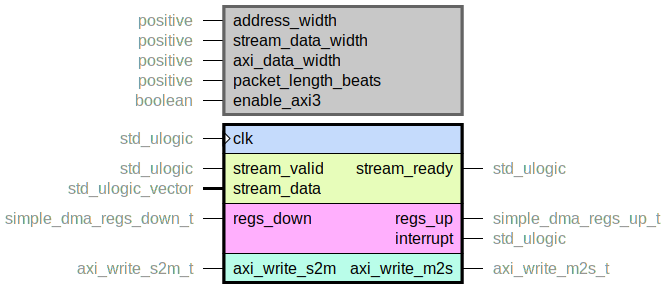

simple_dma_core.vhd

Main implementation of the simple DMA functionality. This entity is not suitable for instantiation in a user design, use instead e.g. simple_dma_axi_lite.vhd.

simple_dma_sim_pkg.vhd

Package with functions to simulate and check the DMA functionality.